# **IN618** Datasheet

Specifications and information are subject to change without notice.

# IN618 Synchronous Multi-node Ultra Low Latency Wireless SoC

#### Key Features

- InPlay SMULL engine

- InPlay proprietary synchronous multi-node communication protocol with ultra-low latency (over-the-air wireless packet travel time) through TDMA and FDMA mechanism

- Bi-directional communication

- Up to 128 nodes in a single network

- Unicast/multi-cast/broadcast mode support

- PHY rate configurable

- User data payload configurable

- Adaptive frequency hopping

- Hierarchical network support

## CPU & memory

- ARM cortex-M4F up to 64MHz with 16KB i-cache

- 256KB ROM (bootloader & SW stack)

- Up to 96KB user SRAM

- 4Kb eFuse memory (Manufacturer ID, Security Key storage)

- 512KB flash memory (Stacked, XIP mode support)

- Over-The-Air Update (OTA) support

- SWD/JTAG debug interface

#### Radio

- 2.4GHz ISM band RF transceiver

- Rx sensitivity -97.5 dBm @ 1Mbps

- Rx sensitivity -94.5 dBm @ 2Mbps

- Tx output 0dBm, 4.1mA, up to +3 dBm

- Rx 5mA

- MedRadio band support (2360MHz~2400MHz)

### Peripheral

- Up to 30 GPIOs

- 2 I2C, master/slave up to 1000kHz clock

- 1 SPI master w/ up to 4 SPI slaves supported, up to 16MHz

- 1 SPI slave, up to 8MHz

- 2 UART up to 2MHz

- 5 dedicated PWMs, up to 13 PWM through I/O configuration

- 1 I2S master and 1 I2S slave, bi-directional stereo support

- 2 PDM mono or 1 stereo with clock range from 160kHz – 5.12MHz

- IS07816

- Keyboard scanner up to 14x14 matrix

- QDEC

- 11-bit ADC, up to 64 KSPS, up to 11 channels

- 8 counters/timers

- Clock sources

- 32MHz crystal, 32.768kHz RTC

- DMA controller

- Up to 2 concurrent DMA streams with 2 channels each

- Voice engine

- Build-in up to 64kHz sampling ADPCM codec, 4:1 compression ratio with 64Kbps mono, 128Kbps stereo for 16kHz sampling rate

- Support PDM to PCM conversion

- PDM or I2S as input

- Sigma-delta audio DAC

#### Security

- HW ECC, AES256, SHA-1, SHA-2

- Secure Boot, Software copyright protection

- True Random Number Generator (FIPS140-2 compliant)

#### Power mode

- Deep Sleep mode 500nA with 32kHz RC ON

- Shutdown mode <20nA

- PMU

- Integrated DCDC buck convertor

- 1.7 3.6V input

- Packaging

- QFN48 6x6mm

- Operating temperature

- -40 ~ +85 °C

#### $\cdot$ Typical applications

- Gaming accessories

- Low latency wireless audio

- Industrial robotic

- Smart classroom

# **About Documentation**

| Document name  | Datasheet                 |                  |

|----------------|---------------------------|------------------|

| Part number    | IN618                     |                  |

| Control number | IN6IDOC-DS-IN618-EN-V1_02 | For external use |

| Revision       | V1.02                     |                  |

| Product status     | Document content                                                 | Data status                                                                                             |  |

|--------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|

| In development     | Objective specification/MRD                                      | Target specification. Revised and<br>supplementary data will be<br>published later                      |  |

| Engineering sample | Specification with measured data on E/S                          | Data based on early E/S sample testing                                                                  |  |

| Customer sample    | Specification with measured data on the early production samples | Data based on early production<br>samples. Revised and<br>supplementary data may be<br>published later. |  |

| Mass production    |                                                                  | Document contains final product specification                                                           |  |

This document applies to the following products:

| Document name   | Applicable products | Product status  |

|-----------------|---------------------|-----------------|

|                 | IN618-Q1-R-G4C0I    | Mass production |

| IN618 Datasheet |                     |                 |

|                 |                     |                 |

|                 |                     |                 |

# **Contents**

| Abo     | ut Documentation                                   | 2    |

|---------|----------------------------------------------------|------|

| 1.      | Product Overview                                   | 8    |

| 2.      | Pin Map Information                                | 10   |

| 2.1.    | QFN48                                              | 10   |

| 3.      | Function Block Description                         | 14   |

| 3.1.    | CPU and memory subsystem                           | 14   |

| 3.2.    | Power system and clocks                            |      |

| 3.2.1.  | Power domains and power operation modes            |      |

| 3.2.2.  |                                                    |      |

| 3.2.3.  | Power supplies                                     | 18   |

| 3.2.4.  |                                                    |      |

| 3.2.5.  |                                                    |      |

| 3.2.5.  |                                                    |      |

| 3.2.5.  |                                                    |      |

| 3.2.5.  |                                                    |      |

| 3.2.5.  |                                                    |      |

| 3.2.5.  |                                                    |      |

| 3.3.    | InPlay SMULL radio and subsystem                   |      |

| 3.4.    | Special function blocks                            | . 25 |

| 3.4.1.  | 11-bit sensor ADC                                  | 25   |

| 3.4.2.  | Hardware security engine                           | 25   |

| 3.4.3.  |                                                    |      |

| 3.4.4.  | Keyboard controller                                | 27   |

| 3.4.5.  | Quadrature decoder                                 | 27   |

| 3.5.    | Peripherals                                        | . 28 |

| 3.5.1.  | I2C                                                | 28   |

| 3.5.2.  | SPI                                                | 28   |

| 3.5.3.  | UART                                               | 29   |

| 3.5.4.  |                                                    |      |

| 3.5.5.  | PDM                                                |      |

| 3.5.6.  |                                                    |      |

| 3.5.7.  |                                                    |      |

| 3.5.8.  |                                                    |      |

| 3.5.9.  |                                                    |      |

| 3.5.10  |                                                    |      |

| 3.5.11. | 5                                                  |      |

| 3.6.    | Programing and debugging interface                 | 31   |

| 3.7.    | User software copyright protection and secure boot | 31   |

| 3.7.1.  | User software copyright protection                 | 32   |

| 3.7.2.                                                                                                                                               | Secure boot                                                                                                                                                                                                                                | 32                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| 4.                                                                                                                                                   | Electronical Characteristics                                                                                                                                                                                                               |                                                                                                    |

| 4.1.                                                                                                                                                 | Absolute maximum ratings                                                                                                                                                                                                                   |                                                                                                    |

| 4.2.                                                                                                                                                 | Recommended operating conditions                                                                                                                                                                                                           | 35                                                                                                 |

| 4.3.                                                                                                                                                 | GPIO PAD characteristics                                                                                                                                                                                                                   | 35                                                                                                 |

| 4.4.                                                                                                                                                 | Buck converter characteristics                                                                                                                                                                                                             | 36                                                                                                 |

| 4.5.                                                                                                                                                 | 11-bit SAR ADC characteristics                                                                                                                                                                                                             | 36                                                                                                 |

| 4.6.                                                                                                                                                 | VBAT monitoring characteristics                                                                                                                                                                                                            | 37                                                                                                 |

| 4.7.                                                                                                                                                 | Device temperature monitoring characteristics                                                                                                                                                                                              | 37                                                                                                 |

| 4.8.                                                                                                                                                 | 32kHz RC oscillator characteristics                                                                                                                                                                                                        | 38                                                                                                 |

| 4.9.                                                                                                                                                 | 32MHz crystal oscillator characteristics                                                                                                                                                                                                   |                                                                                                    |

| 4.10.                                                                                                                                                |                                                                                                                                                                                                                                            |                                                                                                    |

| 4.11.                                                                                                                                                | 32.768kHz RTC oscillator characteristics                                                                                                                                                                                                   |                                                                                                    |

| 4.12.                                                                                                                                                | RF performance characteristics                                                                                                                                                                                                             |                                                                                                    |

| 4.12.1.                                                                                                                                              |                                                                                                                                                                                                                                            |                                                                                                    |

| 4.12.2<br>4.12.3                                                                                                                                     |                                                                                                                                                                                                                                            |                                                                                                    |

| 4.12.3                                                                                                                                               | . RF Transmitter performance characteristics<br>System power consumption                                                                                                                                                                   |                                                                                                    |

| 4.14.                                                                                                                                                | ESD characteristics (all pins)                                                                                                                                                                                                             |                                                                                                    |

|                                                                                                                                                      |                                                                                                                                                                                                                                            |                                                                                                    |

|                                                                                                                                                      |                                                                                                                                                                                                                                            |                                                                                                    |

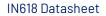

| 5.                                                                                                                                                   | Ordering Information                                                                                                                                                                                                                       |                                                                                                    |

|                                                                                                                                                      |                                                                                                                                                                                                                                            |                                                                                                    |

| 5.                                                                                                                                                   | Ordering Information<br>Packaging                                                                                                                                                                                                          | 47<br>48                                                                                           |

| 5.<br>6.                                                                                                                                             | Ordering Information                                                                                                                                                                                                                       |                                                                                                    |

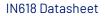

| <b>5.</b><br><b>6.</b><br>6.1.                                                                                                                       | Ordering Information<br>Packaging<br>Package drawing - QFN48                                                                                                                                                                               | <b>47</b><br>48<br>48<br>49                                                                        |

| <b>5.</b><br><b>6.</b><br>6.1.<br>6.2.                                                                                                               | Ordering Information<br>Packaging<br>Package drawing – QFN48<br>IC marking                                                                                                                                                                 | <b>47</b><br><b>48</b><br>48<br>49<br>49                                                           |

| <b>5.</b><br><b>6.</b><br>6.1.<br>6.2.<br>6.3.                                                                                                       | Ordering Information<br>Packaging<br>Package drawing – QFN48<br>IC marking<br>Box package dimension                                                                                                                                        | <b>47</b><br><b>48</b><br>48<br>49<br>49<br><b>50</b>                                              |

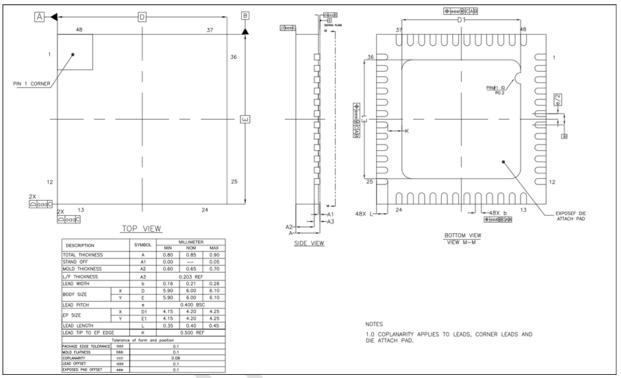

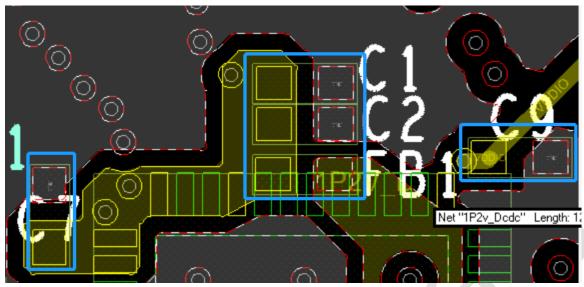

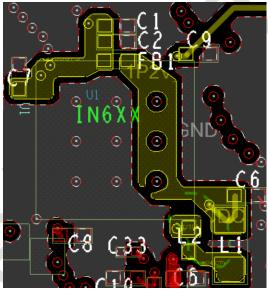

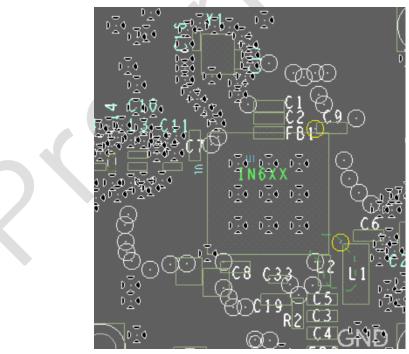

| <ol> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>7.</li> </ol>                                                                                     | Ordering Information<br>Packaging<br>Package drawing – QFN48<br>IC marking<br>Box package dimension<br>Reference Design                                                                                                                    | 47<br>48<br>48<br>49<br>49<br>49<br>50<br>50                                                       |

| <ol> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>7.</li> <li>7.1.</li> </ol>                                                                       | Ordering Information<br>Packaging<br>Package drawing – QFN48<br>IC marking<br>Box package dimension<br>Reference Design<br>IN618 QFN48 reference schematic                                                                                 | 47<br>48<br>48<br>49<br>49<br>49<br>50<br>50<br>50                                                 |

| <ol> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>7.1.</li> <li>8.</li> </ol>                                                                       | Ordering Information<br>Packaging<br>Package drawing – QFN48<br>IC marking<br>Box package dimension<br>Reference Design<br>IN618 QFN48 reference schematic<br>Layout                                                                       | 47<br>48<br>48<br>49<br>49<br>50<br>50<br>50<br>52                                                 |

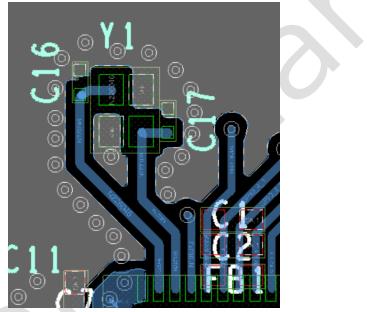

| <ol> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>7.1.</li> <li>8.</li> <li>8.1.</li> </ol>                                                         | Ordering Information<br>Packaging<br>Package drawing - QFN48<br>IC marking<br>Box package dimension<br>Reference Design<br>IN618 QFN48 reference schematic<br>Layout<br>Layer stack-up                                                     | 47<br>48<br>48<br>49<br>49<br>49<br>50<br>50<br>50<br>52<br>52<br>53                               |

| <ol> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>7.1.</li> <li>8.1.</li> <li>8.2.</li> </ol>                                                       | Ordering Information<br>Packaging<br>Package drawing – QFN48<br>IC marking<br>Box package dimension<br>Reference Design<br>IN618 QFN48 reference schematic<br>Layout<br>Layer stack-up<br>Crystal                                          | 47<br>48<br>48<br>49<br>49<br>50<br>50<br>50<br>52<br>52<br>53<br>54                               |

| <ol> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>7.1.</li> <li>8.1.</li> <li>8.2.</li> <li>8.3.</li> </ol>                                         | Ordering Information<br>Packaging<br>Package drawing - QFN48<br>IC marking<br>Box package dimension<br>Reference Design<br>IN618 QFN48 reference schematic<br>Layout<br>Layer stack-up<br>Crystal<br>RF trace                              | 47<br>48<br>48<br>49<br>49<br>49<br>50<br>50<br>50<br>50<br>52<br>53<br>54<br>55                   |

| <ol> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>7.1.</li> <li>8.1.</li> <li>8.2.</li> <li>8.3.</li> <li>8.4.</li> </ol>                           | Ordering Information<br>Packaging<br>Package drawing – QFN48<br>IC marking<br>Box package dimension<br>Reference Design<br>IN618 QFN48 reference schematic<br>Layout<br>Layer stack-up<br>Crystal<br>RF trace<br>Antenna                   | 47<br>48<br>48<br>49<br>49<br>49<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>55<br>55 |

| <ol> <li>6.1.</li> <li>6.2.</li> <li>6.3.</li> <li>7.</li> <li>7.1.</li> <li>8.1.</li> <li>8.2.</li> <li>8.3.</li> <li>8.4.</li> <li>8.5.</li> </ol> | Ordering Information<br>Packaging<br>Package drawing - QFN48<br>IC marking<br>Box package dimension<br>Reference Design<br>IN618 QFN48 reference schematic<br>Layout<br>Layer stack-up<br>Crystal<br>RF trace<br>Antenna<br>PMU LD0 output | 47<br>48<br>48<br>49<br>49<br>50<br>50<br>50<br>50<br>50<br>52<br>53<br>54<br>55<br>55<br>55       |

| 8.9.   | Ground                             | 58 |

|--------|------------------------------------|----|

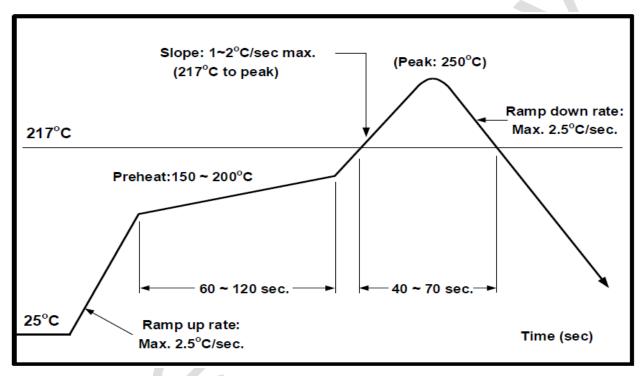

| 9.     | Reflow Profile Information         | 59 |

| 9.1.   | Storage condition                  | 59 |

| 9.1.1. | Moisture barrier bag before opened |    |

| 9.1.2. | Moisture barrier bag open          | 59 |

| 9.2.   | Stencil design                     | 59 |

| 9.3.   | Baking conditions                  | 59 |

| 9.4.   | Soldering and reflow condition     | 59 |

| 9.4.1. | Reflow oven                        |    |

| 10.    | Revision History                   | 61 |

| 11.    | Disclaimer                         | 61 |

# List of Figures

| Figure 1 : Device system block diagram                  | 9  |

|---------------------------------------------------------|----|

| Figure 2 : IN618 pin assignment of QFN48                | 10 |

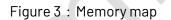

| Figure 3 : Memory map                                   | 15 |

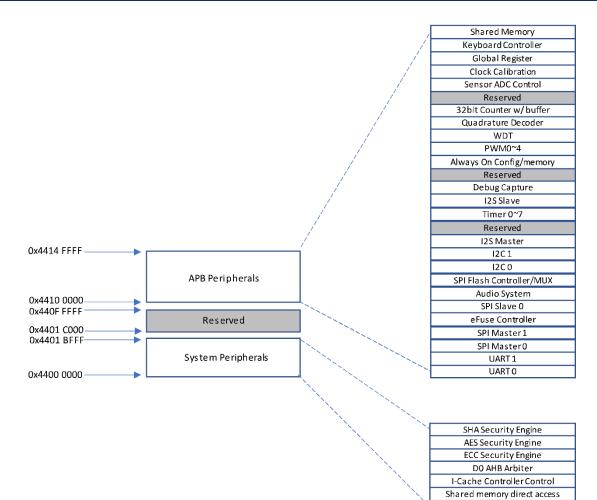

| Figure 4 : Peripheral memory map                        | 16 |

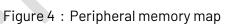

| Figure 5 : Power on sequence requirement                | 17 |

| Figure 6 : Device power supplies                        |    |

| Figure 7 : DCDC buck converter                          | 19 |

| Figure 8 : 32.768kHz crystal                            | 20 |

| Figure 9 : External 32.768kHz source                    | 20 |

| Figure 10 : XO clock source                             |    |

| Figure 11 : 2.4GHz RF transceiver                       |    |

| Figure 12 : InPlay SMULL network topology               | 23 |

| Figure 13 : Frame based communication                   |    |

| Figure 14 : Sensor ADC                                  | 25 |

| Figure 15 : Audio engines                               | 27 |

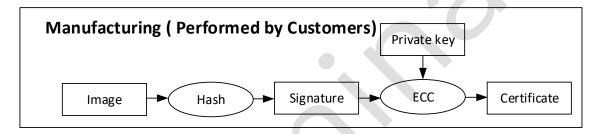

| Figure 16 : Secure software copyright protection        |    |

| Figure 17 : Secure boot                                 |    |

| Figure 18 : Full part number decoder                    | 47 |

| Figure 19 : IN618 QFN48 6mmx6mm package outline drawing | 48 |

| Figure 20 : N618 package marking                        | 49 |

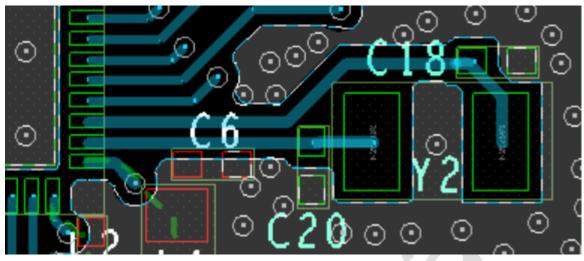

| Figure 21 : IN618 QFN48 reference schematic             | 50 |

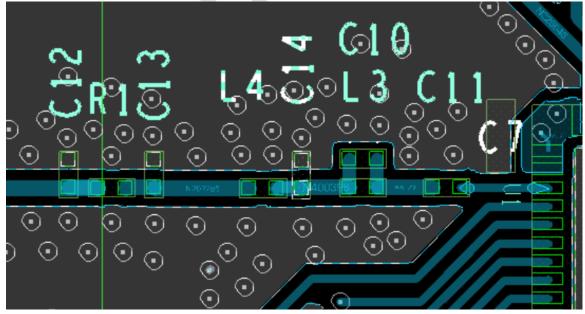

| Figure 22 : 32MHz crystal                               | 53 |

| Figure 23 : 32.768kHz crystal                           | 54 |

| Figure 24 : RF trace                                    | 54 |

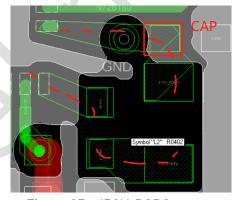

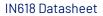

| Figure 25 : IP2V-DCDC output                            | 55 |

| Figure 26 : VBAT trace                                  | 56 |

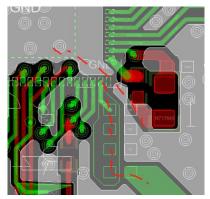

| Figure 27 : Placement with RF power routing             | 57 |

| Figure 28 : Routing of 1P2V supply                      | 57 |

| Figure 29:Thermal pad vias                              | 58 |

| Figure 30 : Example of ground layer                     | 58 |

| Figure 31 : Solder reflow profile                       | 60 |

# List of Tables

| Table 1 : IN618 QFN48 pin description    10                              |

|--------------------------------------------------------------------------|

| Table 2 : GPIO pin mux    12                                             |

| Table 3 : Key information register format    27                          |

| Table 4 : Absolute maximum ratings    34                                 |

| Table 5 : Recommended operating conditions                               |

| Table 6 : GPIO PAD characteristics    35                                 |

| Table 7 : Buck converter characteristics    36                           |

| Table 8 : ADC characteristics    36                                      |

| Table 9 : Vbat monitoring characteristics                                |

| Table 10 : Temperature monitoring characteristics    38                  |

| Table 11 : 32kHz RC oscillator characteristics    38                     |

| Table 12 : 32MHz crystal oscillator characteristics                      |

| Table 13 : 32MHz RC oscillator characteristics    39                     |

| Table 14 : 32.768kHz RTC oscillator characteristics    39                |

| Table 15 : General RF characteristics                                    |

| Table 16 : RF receiver performance characteristics                       |

| Table 17 : RF transmitter performance characteristics         44         |

| Table 18 : System power consumption                                      |

| Table 19 : IN618 6x6 QFN48 package information                           |

| Table 20 : IN618 marking description                                     |

| Table 21 : IN618 package size for reel, inner box and outer box       49 |

| Table 22 : IN618 reference design BOM of QFN4850                         |

| Table 23 : PCB layer stack-up                                            |

|                                                                          |

|                                                                          |

|                                                                          |

|                                                                          |

# 1. Product Overview

**IN618** is InPlay's SMULL SoC product which features synchronous multi-node low-latency protocol stack with 2.4Ghz frequency band RF radio and MCU system integrated. The product integrates a GFSK RF transceiver and PHY which supports up to 2Mbps high data rate.

The device integrates a powerful 32bit ARM Cortex-M4F CPU with floating point unit processing capability. It can operate at various clock rate up to 64MHz. The device has built-in 256KB ROM, up to 512KB Flash memory and high density of SRAM up to 96KB which can be used as application instruction or data space for sophisticated algorithms and applications.

The device has an excellent RF performance with ultra-low power consumption design philosophy in mind, so it is well suited for power constraint applications such as battery powered products (ex. retail beacon and wearables). Along with the powerful ARM Coretex-M4F CPU and rich memory resources integrated into the device, user can develop as many applications without adding additional CPU.

The device has well-crafted hardware security engine designed which supports AES128, AES256, SHA-1, SHA-2 and ECC encryption and decryption algorithms. It also has True Random Number Generator (TRNG) integrated to facilitate security application implementation.

In addition to the sophisticated design on radio and communication modems, the device integrates variety of peripherals such as I2C, SPI, UART, PDM and I2S for user applications. IN618 comes with package option of QFN48.

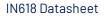

The Figure 1 below shows the system block diagram of SMULL SoC IN618. And features available on the diagram will vary by part number. For more information on available features of different devices, please refer to Ordering Information.

Figure 1 : Device system block diagram

## 2. Pin Map Information

## 2.1. QFN48

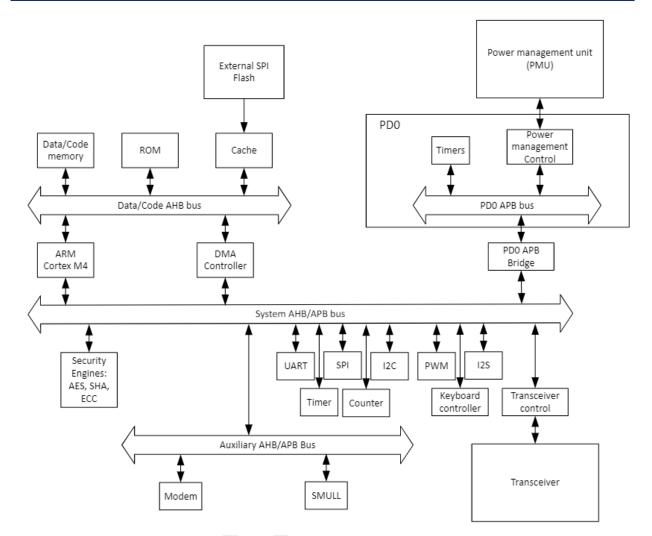

IN618 is offered in an exposed pad 48 pin QFN package. This package has an exposed paddle that must be connected to the system board ground. In *Figure* 2, the QFN package pin assignment is shown.

Figure 2 : IN618 pin assignment of QFN48

| Pin<br># | Pin name    | Pin type     | Description                           |

|----------|-------------|--------------|---------------------------------------|

| 1        | VDD_VCO_2G4 | Analog/RF    | RF VCO power supply 1.2V              |

| 2        | VDD_RF_2G4  | Analog/RF    | RF power supply 1.2V                  |

| 3        | RF_TRX_2G4  | Analog/RF    | RF port                               |

| 4        | VDDQ        | Power supply | eFuse programming voltage supply 3.3V |

| 5        | GPIOD_0_0   | Digital I/O  | Digital signal GPIO_0_0               |

| 6        | GPIOD_0_1   | Digital I/O  | Digital signal GPIO_0_1               |

| 7        | GPIOD_0_2   | Digital I/O  | Digital signal GPI0_0_2               |

#### Table 1 : IN618 QFN48 pin description

| Pin<br># | Pin name  | Pin type         | Description                                |  |  |

|----------|-----------|------------------|--------------------------------------------|--|--|

| 8        | GPIOD_0_3 | Digital I/O      | Digital signal GPIO_0_3                    |  |  |

| 9        | GPIOD_0_4 | Digital I/O      | Digital signal GPI0_0_4                    |  |  |

| 10       | GPIOD_0_5 | Digital I/O      | Digital signal GPIO_0_5                    |  |  |

| 11       | GPIOD_1_0 | Digital I/O      | Digital signal GPIO_1_0                    |  |  |

| 12       | GPIOD_1_1 | Digital I/O      | Digital signal GPIO_1_1                    |  |  |

| 13       | VDDI01    | I/O power        | I/O voltage supply for GPIO power domain 1 |  |  |

| 14       | GPIOD_1_2 | Digital I/O      | Digital signal GPIO_1_2                    |  |  |

| 15       | GPIOD_1_3 | Digital I/O      | Digital signal GPIO_1_3                    |  |  |

| 16       | GPIOD_1_4 | Digital I/O      | Digital signal GPIO_1_4                    |  |  |

| 17       | GPIOD_1_5 | Digital I/O      | Digital signal GPIO_1_5                    |  |  |

| 18       | GPIOD_1_6 | Digital I/O      | Digital signal GPIO_1_6                    |  |  |

| 19       | GPIOD_1_7 | Digital I/O      | Digital signal GPIO_1_7                    |  |  |

| 20       | GPIOD_1_8 | Digital I/O      | Digital signal GPIO_1_8                    |  |  |

| 21       | CHIP_EN   | PMU              | Chip enable                                |  |  |

| 22       | ADC_IN    | PMU              | Sensor ADC input                           |  |  |

| 23       | VBAT      | PMU              | Chip power supply                          |  |  |

| 24       | VSW       | PMU              | DCDC converter switching Node              |  |  |

| 25       | VDD_DCDC  | PMU              | DCDC converter feedback node               |  |  |

| 26       | RTC_X0_P  | PMU              | RTC positive terminal                      |  |  |

| 27       | RTC_XO_N  | PMU              | RTC negative terminal                      |  |  |

| 28       | GPIOM_2_0 | Mixed signal I/O | Mixed signal GPI0_2_0                      |  |  |

| 29       | GPIOM_2_1 | Mixed signal I/O | Mixed signal GPI0_2_1                      |  |  |

| 30       | GPIOM_2_2 | Mixed signal I/O | Mixed signal GPIO_2_2                      |  |  |

| 31       | GPIOM_2_3 | Mixed signal I/O | Mixed signal GPI0_2_3                      |  |  |

| 32       | GPIOM_2_4 | Mixed signal I/O | Mixed signal GPI0_2_4                      |  |  |

| 33       | GPIOM_2_5 | Mixed signal I/O | Mixed signal GPI0_2_5                      |  |  |

| 34       | GPIOM_2_6 | Mixed signal I/O | Mixed signal GPI0_2_6                      |  |  |

| 35       | GPIOM_2_7 | Mixed signal I/O | Mixed signal GPI0_2_7                      |  |  |

| 36       | GPIOM_2_8 | Mixed signal I/O | Mixed signal GPI0_2_8                      |  |  |

| 37       | VDDI02    | I/O power        | I/O voltage supply for GPIO power domain 2 |  |  |

| 38       | GPIOD_3_2 | Digital I/O      | Digital signal GPI0_3_2                    |  |  |

| 39       | GPIOD_3_3 | Digital I/O      | Digital signal GPIO_3_3                    |  |  |

| 40       | GPIOD_3_4 | Digital I/O      | Digital signal GPI0_3_4                    |  |  |

| 41       | GPIOD_3_5 | Digital I/O      | Digital signal GPIO_3_5                    |  |  |

| 42       | GPIOD_4_0 | Digital I/O      | Digital signal GPIO_4_0                    |  |  |

| Pin<br># | Pin name  | Pin type      | Description                                   |  |

|----------|-----------|---------------|-----------------------------------------------|--|

| 43       | GPIOD_4_0 | Digital I/O   | Digital signal GPIO_4_1                       |  |

| 44       | TEST_MODE | Digital input | Test mode selection, GND for normal operation |  |

| 45       | VDD_AMS   | Analog/RF     | AMS Supply 1.2V                               |  |

| 46       | XO_N      | Analog/RF     | X0 positive terminal                          |  |

| 47       | XO_N      | Analog/RF     | X0 negative terminal                          |  |

| 48       | VDD_PLL   | Analog/RF     | RF PLL power supply 1.2V                      |  |

*Table* 2 shows the Pin Mux configuration that developers can use to configure the I/O functionality based on application needs. Only one Pin Mux option can be chosen and once configured, the chip I/O functionality will be fixed based on the configuration.

| Pin<br># | Pin<br>Name  | Mux 1              | Mux 2               | Mux3                         | Mux4             | Mux5                | Mux6                |

|----------|--------------|--------------------|---------------------|------------------------------|------------------|---------------------|---------------------|

| 5        | GPIO_0<br>_0 | Uart_1_rts         | Keyboard_<br>O      |                              | l2c_0_scl        |                     | Pwm_0               |

| 6        | GPI0_0<br>_1 |                    | Keyboard_<br>1      | Spi_mstr_<br>miso_bkup<br>-1 | l2c_0_sda        |                     | Pwm_1               |

| 7        | GPI0_0<br>_2 | Uart_0_tx          | Keyboard_<br>25     |                              |                  |                     | Pwm_2               |

| 8        | GPI0_0<br>_3 | Wlan_tx_b<br>kup-0 |                     | Spi_mstr_<br>mosi_bkup       | l2c_1_scl        | Audio_sd_l<br>_bkup | Tx_en1              |

| 9        | GPI0_0<br>_4 | Wlan_rx_b<br>kup-0 | Keyboard_<br>4      | Spi_mstr_<br>clk_bkup        | l2c_1_sda        | Audio_sd_<br>r_bkup | Tx_en1_bk<br>up     |

| 10       | GPI0_0<br>_5 |                    | Keyboard_<br>22     |                              |                  |                     |                     |

| 11       | GPIO_1_<br>0 | Uart_0_rx-<br>1    | Keyboard_<br>24     |                              |                  |                     | Swd_trace<br>_clk-0 |

| 12       | GPI0_1_<br>1 | Jtag_tms_<br>swdio |                     |                              |                  |                     |                     |

| 14       | GPI0_1_<br>2 | Jtag_tcks<br>ck-1  |                     |                              |                  |                     |                     |

| 15       | GPIO_1_<br>3 | Jtag_tdo           | Keyboard_<br>O_bkup | Qd_0_cha_<br>x-0             | l2s_mstr_c<br>lk | l2s_slv_clk<br>-0   | Swd_trace<br>_swo   |

| 16       | GPI0_1_<br>4 | Jtag_tdi-1         | Keyboard_<br>1_bkup | Qd_0_chb_<br>x-0             | l2s_mstr_<br>ws  | l2s_slv_ws          |                     |

| 17       | GPIO_1_<br>5 | Uart_1_rts         | Keyboard_<br>2_bkup | Qd_0_idx_<br>x-0             | l2s_mstr_s<br>d0 | l2s_slv_sd<br>0     | Swd_trace<br>_0     |

Table 2 : GPIO pin mux

| Pin<br># | Pin<br>Name   | Mux 1                | Mux 2               | Mux3               | Mux4                | Mux5             | Mux6                 |

|----------|---------------|----------------------|---------------------|--------------------|---------------------|------------------|----------------------|

| 18       | GPIO_1_<br>6  | Uart_1_cts<br>-1     | Keyboard_<br>3      | Qd_O_cha_<br>y-O   | l2s_mstr_s<br>d1    |                  | Swd_trace<br>_1      |

| 19       | GPI0_1_<br>7  | Uart_1_tx            | Keyboard_<br>4_bkup | Qd_0_chb_<br>y-0   | l2c_0_scl_<br>bkup  | l2s_slv_sd<br>O  | Swd_trace<br>_2      |

| 20       | GPIO_1_<br>8  | Uart_1_rx-1          | Keyboard_<br>5_bkup | Qd_0_idx_<br>y-0   | l2c_0_sda<br>_bkup  | Pwm_4            | Swd_trace<br>_3      |

| 28       | GPI0_2<br>_0  |                      | Keyboard_<br>5      |                    |                     |                  |                      |

| 29       | GPI0_2<br>_1  | Uart_1_tx_<br>bkup   | Keyboard_<br>2      | Spi_mstr_<br>ssn0  | Counter_0           | Audio_sd_l       | Tx_en_bku<br>p       |

| 30       | GPI0_2<br>_2  |                      | Keyboard_<br>19     |                    | Counter_1           |                  |                      |

| 31       | GPI0_2<br>_3  | Uart_0_tx_<br>bkup   |                     | Qd_0_cha_<br>z-0   | Counter_2           | Audio_sd_<br>r   | Rx_en_bku<br>p       |

| 32       | GPI0_2<br>_4  |                      | Keyboard_<br>18     |                    | Counter_3           |                  |                      |

| 33       | GPI0_2<br>_5  | Uart_0_rx_<br>bkup-1 | Keyboard_<br>20     | Qd_0_chb_<br>z-0   | Counter_4           | 32kHz_clk        | Rx_en                |

| 34       | GPI0_2<br>_6  |                      |                     |                    | Counter_5           |                  |                      |

| 35       | GPI0_2<br>_7  | Uart_1_rx_<br>bkup-1 | Keyboard_<br>23     | Tv_infrd_o<br>ut   | Counter_6           |                  | Pdm_1_dat<br>a-0     |

| 36       | GPI0_2<br>_8  |                      | Keyboard_<br>3_bkup |                    | Counter_7           |                  | Pdm_0_da<br>ta-0     |

| 38       | GPI0_3<br>_2  |                      | Keyboard_<br>27     | Spi_mstr_<br>ssn3  | Wlan_tx-0           |                  | Wdt_reset            |

| 39       | GPIO_3<br>_3  |                      | Keyboard_<br>26     | Spi_mstr_<br>ssn3  | Wlan_rx-0           |                  | Wdt_reset<br>_bkup   |

| 40       | GPI0_3<br>_4  | Spi_mstr_<br>clk     |                     | Spi_slv_clk<br>-0  | Ble_active          | Qd_0_idx_<br>z-0 | Tx_en                |

| 41       | GPI0_3<br>_5  | Spi_mstr_<br>miso-1  |                     | Spi_slv_mi<br>so   | Ble_active<br>_bkup | Qd_0_led_<br>x   | 32m_clk_o<br>ut_bkup |

| 42       | GPI0_4<br>_0  | Spi_mstr_<br>mosi    | Keyboard_<br>21     | Spi_slv_m<br>osi-1 | l2c_1_scl_<br>bkup  | Qd_O_led_<br>y   | Pdm_0_clk            |

| 43       | GPI0_4<br>_1  | Spi_mstr_<br>ssn0    |                     | Spi_slv_ss<br>n-1  | l2c_1_sda_<br>bkup  | Qd_0_led_<br>z   | 32m_clk_o<br>ut      |

| 44       | TEST_M<br>ODE |                      |                     |                    |                     |                  |                      |

## **3. Function Block Description**

## 3.1. CPU and memory subsystem

The device integrates a powerful ARM Cortex-M4F processor core and their associated busses and memories. The Coretex-M4F processor incorporates a processor core, Nested Vectored Interrupt Controller (NVIC), high performance bus interfaces and a Floating-Point Unit (FPU).

The core processor has 16KB instruction cache memory. This subsystem also includes two independent DMA controllers with 4 channels each, 80KB of SRAM and 256KB of ROM. The subsystem integrates a hardwired cryptographic engine which is associated with the boot loader system to provide a secure boot implementation. This includes both system integrity check and authentication check of the application software. The advanced architecture design of system buses provides the exclusivity of access to radio communication blocks at the same time the flexibility of access to other peripheral blocks without sacrificing the system performance and stability. Active power consumption of the Cortex-M4F is 45uA/MHz at 3.3V as chip supply voltage with the built-in buck converter enabled and 1.2V as core supply voltage.

There are two DMA controllers with 2 channels each. They support independent accesses to peripherals using AHB bus to copy data from data/instruction memory to the peripheral memories or vice versa.

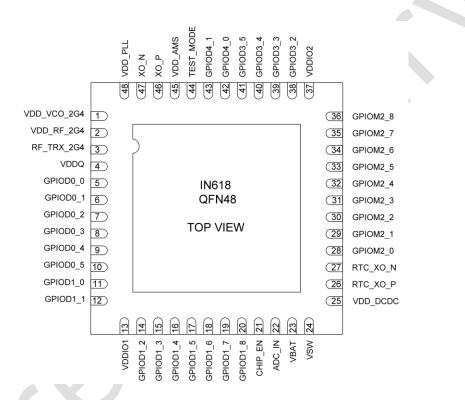

There is 96KB of SRAM memory, which can be fully retained or retained in increments of user defined blocks as small as 4KB. Among the 96KB of SRAM memory, 16KB can be used as cache memory for XIP (execute-in-place) flash memory controller.

There is 256KB of ROM memory that contains boot loader and Bluetooth 5 protocol stack. The device also integrates a 512KB or 1MB flash memory (part number dependent) for user program and data storage. The device supports XIP (execute-in-place) mode for the flash memory so that user can directly execute the program from flash memory rather than copying it into SRAM to run.

The device has integrated 4Kb of eFuse memory that can be used as security key storage and manufacture ID etc. Once the eFuse memory is being programmed and locked, the content of the memory will become permanent and cannot be modified or changed.

See Figure 3 and Figure 4 for the memory map in detail.

www.inplay-tech.com

DMA Control 0~1

## 3.2. Power system and clocks

#### 3.2.1. Power domains and power operation modes

The power system provides assurance that power supplies for each respective operation mode or blocks are provided with correct timing and voltage.

The device has the following power domains: AONPD (always-on power domain, also referred as PD0 domain), DOOPD (dynamic ON-OFF power domain, also referred as PD1 domain), and seven data/instruction memory banks, which can be in active, retention, or power-down mode.

Some power operation modes are listed as followings:

- Chip deep sleep mode. Only the AONPD domain is enabled. All other domains are closed. In this mode, the sleep timer is running, and the timer decides when to wake up the other domains. This mode can also be awakened by external wake-up pins or brownout detection trigger events.

- Chip sleep mode and memory retention mode. AONPD is turned on to retain the contents of a certain memory bank. For example, one of the modes is a reserved mode with a 4kB memory bank. This mode is where the radio works in a sleep state for simple task operations such as advertising or where there is only one connection and the radio works in a sleep state in the most power-efficient manner.

- Chip active mode. All power domains are on.

- Chip off mode. All chip blocks are in a state of power off. The leakage current in this mode is less than 20nA.

#### 3.2.2. Power sequence

The power sequence should follow the sequence as shown in *Figure* 5.

Figure 5 : Power on sequence requirement

#### 3.2.3. Power supplies

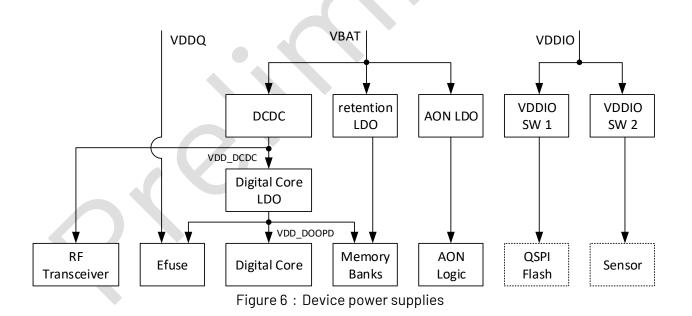

*Figure* 6 shows the power supply architecture for different power domains and blocks. The device has multiple power supplies which including VBAT, VDDIO, and VDDQ. Inside Device, it has a buck DCDC converter, an AONPD LDO, a retention LDO, and two VDDIO switches.

- The AONPD logic is powered by the AONPD LDO.

- The DCDC powers the RF transceiver and the digital core (including the CPU, the digital part of the transceiver, the eFuse, the peripherals) through a digital LDO.

- The memory bank is powered by the digital core LDO in active operation mode and by the retention LDO in sleep mode.

- The two VDDIO switches (VDDIO SW1 and SW2) provide power to the stacked flash memory and external circuits such as sensors. In sleep mode, these two switches can be configured to be turned off to reduce leakage power.

- VDDQ is used to program the eFuse memory. It is only needed for eFuse programming. When do the eFuse programming, VDDQ and VDDIO must be 3.3V ± 10%.

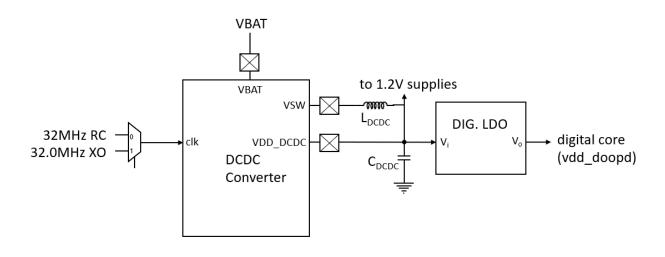

#### 3.2.4. DCDC converter

The buck DCDC converter, as shown in *Figure* 7 efficiently reduces the voltage of the battery to around 1.2V. The 1.2V supply is used to power the radio transceiver directly. In addition, it is used as the input to a LDO that in turn creates the supply for the digital core. Two external components

are required for the DCDC converter, an inductor and a capacitor. The recommended values are 10uH and 1uF, respectively. Other values are permitted; however, they will affect the behavior of the DCDC in terms of efficiency, startup time, and ripple amplitude.

#### 3.2.5. Clock system

The device's clock system is designed to provide clocks to all subsystems that require clocks and for switching between different clock sources without degrading system performance or power consumption.

There are five types of clock sources. They are RC 32kHz, RTC 32.768kHz, RC 32MHz, X032/64MHz, and Programmable CLK from the clock PLL. RC 32kHz is the default clock for the AONPD.

#### 3.2.5.1. RC 32kHz

The RC32kHz clock is a low frequency clock for AONPD logic. This clock is the default clock source for the AONPD during cold boot. If the eFuse memory configuration indicates that an RTC crystal is installed, the boot code will switch the AONPD clock source to an RTC clock.

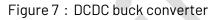

### 3.2.5.2. RTC 32.768kHz

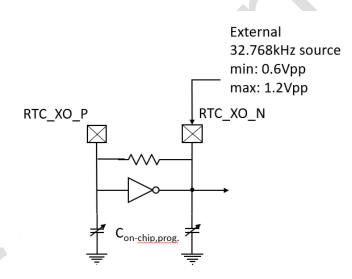

At cold boot, RC 32kHz is the default clock for AONPD. After cold boot, the bootrom code will enable the RTC clock if an RTC crystal is installed, and switch to RTC 32.768kHz as the default clock for AONPD. *Figure* 8 shows a block diagram of 32.768kHz crystal.

Figure 8: 32.768kHz crystal

The device also supports external 32.768kHz clock source as input as shown in Figure 9.

The RTC clock can be muxed out to a GPIO pin that user can use for their applications.

#### 3.2.5.3. RC 32MHz

RC32MHz is a 32MHz high frequency ring oscillator which provides clock source while the crystal oscillator is starting up. CPU will use RC 32MHz by default after code boot or wake-up from sleep mode and SW may switch to XO clock after XO becomes stable.

#### 3.2.5.4. X0 clock

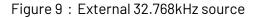

XO clock is high frequency clock source in 32MHz. XO clock is sourced from an external 32MHz crystal as shown in *Figure* 10. XO is controlled by AONPD and is enabled by default after cold boot. The bootloader should switch between the CPU clock and peripheral clock from RC 32MHz to XO 32MHz. This is important for the bootloader as the bootloader may try to get an image from UART interface which requires a more accurate clock source. Inside the chip, we also have one XO doubler which produces the XO 64MHz clock.

Figure 10 : XO clock source

#### 3.2.5.5. CLK PLL

Clock PLL is designed to provide multiple clock frequencies for different clock requirements for the radio transceiver on different PHY rate receptions. By default, CLK PLL is automatically controlled by the hardware.

## 3.3. InPlay SMULL radio and subsystem

The device incorporates an InPlay SMULL radio and subsystem that contains the RF transceiver, baseband, PHY and link layer engines.

The physical layer has the digital PHY and RF transceiver that transmits and receives GFSK packets at 2Mpbs. The PHY can also be configured to 1Mbps mode to transmits and receives 1Mbps modulated packets.

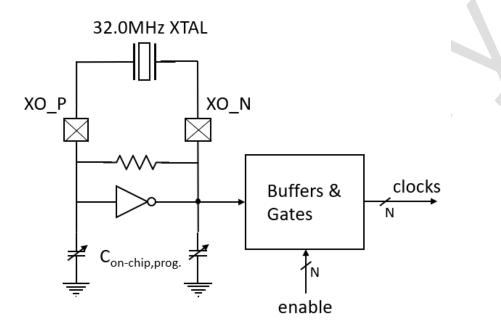

The 2.4GHz transceiver has one chip pin, RF\_TRX\_2G4, for both the transmission and reception of RF signals, as shown in *Figure* 11. An on-board matching network is recommended to get the best RF performance out of the device. It is possible for the matching network to favor the RX path over the TX path or vice-versa, but the recommended matching network in the reference design is a balance of both paths. There are four supply pins for the 2.4GHz transceiver, that are nominally 1.2V. They should normally be connected to the DCDC output, VDD\_DCDC. The transceiver needs a 32.0MHz crystal oscillator reference. To reduce BOM cost, the CI for the crystal is integrated on-chip. The on-chip XO load capacitance CI can be programmed with registers from 0.5pF to 8pF in 0.5pF steps.

Figure 11 : 2.4GHz RF transceiver

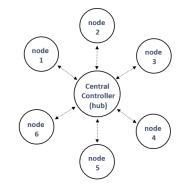

The baseband controller combines both hardware and software implementation that supports variety of communication modes between master and slave devices: Unicast, multi-cast and broadcast modes. In a typical start topology network, as shown in *Figure* 12, the central node will operate as the master and the peripheral nodes will operate as the slave nodes. The communication between the master and the slaves can be unidirectional or bi-directional.

Figure 12 : InPlay SMULL network topology

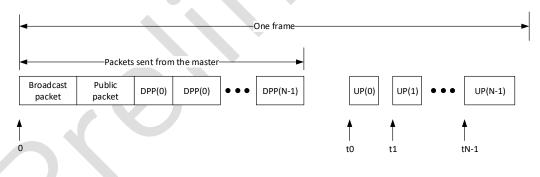

The baseband controller can be configured as either master or slave operation mode. The communication between the master and the slaves is framed based communication as shown in *Figure* 13. On each frame, the master sends a broadcast packet, or a public packet, or a downlink private packet (DPP) to each of the slaves. As illustrated in *Figure* 13, assume there are N slaves, and each slave has a unique ID number from {0, 1, 2, ..., N-1}. Each salve can send an uplink private packet at the assigned time (t0, t1, ...,) in the frame to the master. The packets sent from the master share the same preamble and sync address. Each packet from the slave has its own preamble and sync address.

And all the timing critical functions in the baseband controller are implemented in hardware such as CRC, data whitening and access address detection.

Figure 13 : Frame based communication

The data exchange can be configured to operate in three different modes between a master and multiple salves.

#### - Private data exchange mode

The master can be configured to send each slave a private packet at each frame. Each slave can be configured to send the master a private packet at each frame.

Private packet: There is acknowledgement between the sender and the recipient.

#### - Public data exchange mode

The master can be configured to send a public packet to all the slaves at each frame.

Public packet: The slaves do the acknowledgement. The master does not proceed to next public packet unless the current public packet is acknowledged by all the slaves.

#### Broadcasting mode

The master can be configured to send a broadcast packet to all the slaves at each frame. Broadcast packet: Slaves do not acknowledge the reception of a broadcast packet.

## 3.4. Special function blocks

#### 3.4.1. 11-bit sensor ADC

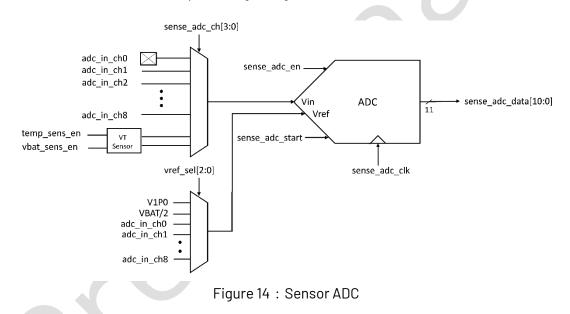

The device has a sensor ADC block as shown in *Figure* 14 which user can use for converting analog signals to digital domain signal for CPU processing.

The sensor ADC has 11 physical bits and can convert at a maximum of 64 KSPS. The actual clock speed and conversion rate are controlled through digital settings. The input to the ADC is preceded by a multiplexer which enables the user to sample up to 11 different channels (package option dependent). In addition, the ADC can be used to measure the internal VBAT voltage level or the temperature. The digital control system for the ADC gives the user the flexibility to choose which channels are sampled in what order. The required voltage reference (Vref) to the ADC can be selected from multiple sources, including an on-chip 1.0V reference, the VBAT voltage divided by 2, or external channels. The input voltage range to the ADC shall be between 0V and 2\*Vref.

#### 3.4.2. Hardware security engine

The device integrates a set of cryptographic engines which comprise of hardware accelerator to compute AES, SHA and ECC algorithms. Such engine can be used by user for application that requires strong security system implementation.

The AES module implements AES encryption and decryption algorithm as defined by the NIST FIPS Publication 197. The features supported by this block are.

- Key length supported are 128b, 192b and 256b and is configurable.

- The authentication modes being supported are XCBC, F8, CMAC, CCM, CBC, CTR and ECB mode.

The SHA module implements hash algorithm and supports SHA-1 and SHA-2.

The ECC module implements ECC encryption and decryption algorithm. The key length supported are 128b, 192b and 256 bits.

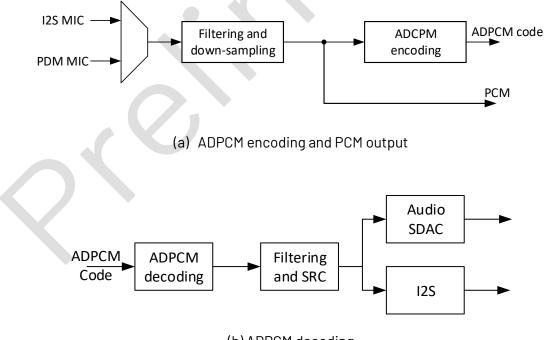

#### 3.4.3. Audio ADPCM and resampling engines

The device has ADPCM and audio sampling rate conversion (SRC) engines which can be used to support and develop wireless voice and audio applications.

The audio engine takes the audio data input from either PDM or I2S interfaced microphone then do the ADPCM encoding and wrapper for transmission through radio interface as shown in *Figure* 15 (a). The ADPCM engine can be bypassed, in that case, we can have raw 16-bit PCM sample outputs.

The received ADPCM coded data through radio interface can also be passed to the ADPCM decoding, and the be played through the Sigma-Delta DAC (SDAC) or I2S as shown in *Figure* 15(b).

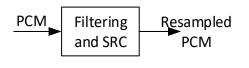

The device's audio SRC can be also to be used for direct PCM sample rate conversion (such as conversion for audio between sampling rate 44.1kHz and 48kHz) as shown in *Figure* 15(c).

(b) ADPCM decoding

(c) Audio SRC

Figure 15 : Audio engines

#### 3.4.4. Keyboard controller

The device has a keyboard controller module that scan through the columns or rows to identify each key's row/column index.

User can define the scan interval and scan through all columns/rows every 0.5, 1, 2 or 4 milliseconds. Every time after the scan, if any key status has been updated, an interrupt will be generated to notify the CPU. At the same time, following information will be stored in the status registers:

#### Table 3 : Key information register format

| 1 bit (press/release) | 1 bit (multi-key event) | 28 bits(X/Y index) of the key |

|-----------------------|-------------------------|-------------------------------|

The first bit indicates if the key is pressed or released during the scan. The second bit indicates if the multi-key event happens (used to support multiple key pressed/released at the same time). If this bit is asserted, the second status register (same format as the first one) will be populated. If this bit in the second register is also set, the third register will be populated, and so on. At most 4 key status registers will be stored. The last field in the registers is used for column/row index of the key. The number of GPIO's used for columns and rows can be configured through control registers. The number of regular keys and special keys (such as shift, control, alt, home, end, etc.) can be configured through control register and maximal number of supported keys is 108.

Based on the control registers setting, the de-bounce filter can filter out glitches in the range of 0 (de-bounce feature disabled) to 63 milliseconds (in the step of 1ms). The press and release debounce filer can have different glitch filtering time value.

All keyboard interrupts will be listed as parallel I/O ports as a standard interrupt controller (including pulse-to-level conversion, masks, clears features) will be used to combine these interrupts to a single interrupt to CPU. All keyboard control and status registers will be used to convert these signals to control/status registers accessible through APB interface to CPU.

#### 3.4.5. Quadrature decoder

The device has a Quadrature Decoder with which user can interface the device to a mechanical to electronical rotary device such as servo motor, volume control wheels and PC mice etc. The

decoded quadrature signals are used as data input to system to determine the absolute or relative position of the rotary device.

The quadrature decoder comprises of Signal\_A, Signal\_B and Signal\_LED as interface pins to external rotary device. Signal\_A and Signal\_B are input signals from external quadrature encoder to indicate movement of the rotary device. Signal\_LED is an optional output signal to external quadrature encoder and will be asserted a few microseconds (defined through control registers) before the sampling and de-asserted immediately after Signal\_A, Signal\_B values are being sampled by the decoder.

An optional de-bounce filter can be enabled. The Signal\_A and Signal\_B values are only valid if their values are constants during the de-bounce filter window (which is the same length as the sampling interval). If there is value change in the de-bounce filter window, the Signal\_A/Signal\_B value will be ignored and keep the same values as the previous sampling. When the de-bounce filter and Signal\_LED are enabled, the Signal\_LED will keep asserted during the de-bounce filter window and the Signal\_A and Signal\_B values are kept being sampled.

## 3.5. Peripherals

#### 3.5.1. I2C

I2C is a simple two-wire bus with a software defined protocol for system control and peripherals. It has a serial data (SDA) and a serial clock (SCL). The device has two independent I2C interfaces (package dependent). The maximum I2C clock rate being supported is 1MHz.

I2C can be configured to operate in either master or slave mode. User has the flexibility to determine and program the slave I2C address. It has 7bit addressing. The slave address is transferred in the first byte after the Start condition. The first seven bits of the byte comprise the slave address with the eighth bit indicating R/W flag ("1" for read and "0" for write). It supports bulk transmit mode.

The I2C has access to the DMA Controller and the data can be moved between CPU memory and peripheral buffer through DMA.

#### 3.5.2. SPI

SPI is a four-wire serial peripheral interface bus commonly used to send data between microcontroller and peripherals. It comprises a clock (SCK) and data lines (MOSI, MISO) along with a chip select line (SS).

The device has two SPI interfaces. They both can be configured to operate on either master mode or slave mode. In master operation mode, the maximum clock rate supported is 16MHz. In the

master mode, the device can support up to 4 independent slaves using different SS line while sharing the same SCK, MOSI and MISO lines. It may also support dual-SPI and quad-SPI mode operation in the master mode to increase the throughput.

In the slave mode, the device can operate on SCK clock rate of no higher than 8MHz.

SPI has access to DMA Controller and the data can be moved between CPU memory and SPI peripheral buffer through DMA.

#### 3.5.3. UART

The device includes two UART cores which supports universal asynchronous transmitter/receiver function and support programmable baud rate up to 2Mbps. The two UART cores are time-multiplexed to 4 UART interfaces (package dependent).

The UART has built-in 16bytes of transmit and receive data FIFO and support auto flow control. The UART has access to the DMA Controller and the data can be moved between CPU memory and UART buffer FIFO buffer through DMA.

#### 3.5.4. Counter/timer/PWM

The device has one 32bit counter which run on the 32MHz XO clock (or divided version of the 32MHz), one 32kHz 32bit counter, and 4 flexibly configurable counters.

The 4 flexibly configurable counters can be used to capture values (and the time duration) of the external slow signals. They can also be used to send signals out based on the configuration registers. They can be used for Infrared remote control (including learning and transmitting) and ISO-7816 protocol. They can also be used for other features such as frequency estimate of external signals, clock generation, delay timing, etc. They can also be chained together to create more complicated signals.

The device has two Sleep Mode Timers. Both can be used by user for implementing Timer functionality in a lower power fashion without waking up the CPU until Sleep Timer Event expires. The clock source for the Sleep Mode Timer can be either from internal RC 32kHz clock or external RTC 32.768kHz clock.

The device has five Pulse Width Modulators (PWMs) with programmable output frequency and duty cycle. The clock source can be from 2MHz up to 32MHz which will provide high resolution of output frequency.

#### 3.5.5. PDM

The device has a PDM interface which can convey audio data digitally over a CLK (clock)/PDM (PDM bit stream) pair. The device supports both mono stream and stereo stream of input from an

external PDM peripheral with multiple PDM clock rate support from 160kHz to 5.12MHz. The PDM bit stream is clocked at a single edge (selectable) for mono stream or clocked at both edges for stereo stream. After filtering and down-sampling, 16-bit PCM stream will be generated which can be further converted to 4-bit ADPCM format.

#### 3.5.6. I2S

The I2S bus is a simple three-wire serial bus protocol used for connecting digital audio devices together. It has SCK (bit clock), WS (Word Select) and SD (serial multiplexed data line). It supports to operate on either master or slave mode. In master I2S mode, the WS clock rate supported are 7.8125kHz, 8kHz, 15.625kHz, 31.25kHz and 46.875kHz. WS clock rate by default is 15.625kHz. The SCK clock supports from a few hundred kHz to 3.2MHz.

The device has two I2S interface. One is master I2S and the other is slave I2S. Both I2S cores support bi-directional data transfer.

The I2S has access to DMA Controller and the data can be moved between CPU memory and I2S data memory through DMA.

#### 3.5.7. Cache and execution-in-place (XIP)

The chip provides a 2-way set associative instruction cache capability for stacked SPI flash to reduce the potential latency due to slower speed on the SPI interface. The cache can support up to 2M bytes of the SPI flash address spaces. The cache data/tag memories can be retained during sleep to speed up wake up CPU execution.

#### 3.5.8. DMA

The chip provides 2 independent DMA controllers and each controller connects to 12 different peripheral interfaces. Each controller also provides 2 parallel channels which can be enabled simultaneously. The DMA controllers supports data copy between peripheral buffers, shared memories and the CPU data memories. All channels in the DMA controllers supports multi-block DMA transfers.

### 3.5.9. WDT

A programmable WDT is provided, and its timeout signal is connected to Cortex M4 non-maskable interrupt (NMI) source. The second timeout signal from WDT can also be programmed to be sent through chip pins (polarity programmable) for external hardware logic to reset the chip. It can also be sent out as a periodic waveform as preprogramed in PWM block. The same signal can also be programmed to reset the whole chip automatically or switchable power domain.

#### 3.5.10. Audio encoder/decoder

Simple adaptive differential pulse-coded modulation (ADPCM) audio encoder/decoder is provided as low-quality audio digital MIC/speaker interface. Multiple commercial ADPCM packet formats

including Microsoft and Apple are supported. Raw PCM format data from digital MIC interface (through PDM or I2S) is also provided and available to CPU processing through DMA or manually memory read.

#### 3.5.11. GPIO and analog I/O

The device supports up to 30 GPIOs (package dependent) and a dedicated analog input pin (package dependent). There are two types of GPIOs: mixed signal GPIOs and digital general purpose IOs. A mixed signal GPIO can be configured as a digital GPIO or be configured as an analog signal input pin for Senor ADC.

Each GPIO has a programable pullup or pulldown resistor when it is in digital input mode and has a 2-level programmable output driving strength options.

Each GPIO can be configured as a wakeup pin, and the polarity of each wakeup signal can be programmable to "high" or "low".

The device supports GPIOs' state retention during sleep.

All GPIOs support asynchronous interrupts. They can be configured as interrupt sources to the ARM core. Multiple of GPIOs' inputs can be grouped together to form a single interrupt. For each GPIO's input, we can configure its polarity, and its mask.

When CHIP\_EN (chip enable) is low, the device is in shutdown mode and all the GPIO(s) are in high Z output state. When the chip is enabled, all the GPIOs are in input mode by default (with pull-up enabled). After boot, the SW may program the GPIOs as appropriate modes (like input/output/high Z state or analog input).

## 3.6. Programing and debugging interface

Debug and trace functions are integrated into the device. Serial Wire Debug (SWD) and JTAG (Trace functions) are supported.

Note that SWD and JTAG will be disabled once an eFuse bit (the JLINK disable bit) is programmed to be 1, and there will be no access allowed by and from external debugging tools.

## 3.7. User software copyright protection and secure boot

Often, for a system with a flash memory, there are two concerns. The first concern is to how to protect the IPs on the flash memory. To protect IPs on the flash memory, one of popular approaches is to encrypt the code. The second concern is that we need to make sure the image on the flash is an authenticate image. To resolve the second concern, secure booting is required.

The device supports flash encryption and secure booting which can be used to protect user's IP and authenticate the image before it is executed.

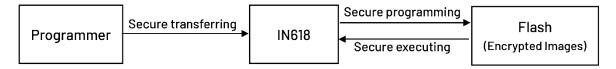

#### 3.7.1. User software copyright protection

The device has a dedicated encryption engine that protects the user's software intellectual property. It supports secure file transfer from programmer to device, as shown in *Figure* 16. When a programmer attempts to program the device's flash memory, the program and the device's bootrom can negotiate a shared key through the ECDH (Elliptic-Curve Diffie-Hellman) key exchange protocol. The key can then be used to encrypt the firmware image file as the programmer transfers it to the device. The encryption is based on AES-256.

The device has a dedicated random number generator. Each time the key is negotiated with the programmer, it will use a different random number. As a result, the different device will have different keys at different times.

Figure 16 : Secure software copyright protection

The firmware image file stored on the flash memory can be configured to be encrypted or unencrypted fashion. If choose to be encrypted, when the device's bootrom gets an encrypted image from the programmer, it first decrypts the image file, and then re-encrypts the image using different key generated through secure programming key generator engine. The newly encrypted image will be programmed to the flash memory. Such procedure is being defined as secure programing.

Two types of flash encryption are supported: One is AES-256 encryption. When executing the AES-256 encrypted code, the bootrom will first decrypt the encrypted code using a secret key tied with device's unique ID and put the decrypted code on the device's internal RAM. Another type of encryption is InPlay's Proprietary Real-Time Encryption (PRTE) which can be decrypted on real-time code execution. An image can be configured to be partly AES-256 encrypted, partly InPlay's PRTE encrypted, or partly non-encrypted. The encryption keys are tied with the device's unique ID. Thus, the same encrypted code will not be executed on two different devices. We call such code execution on the device secure executing.

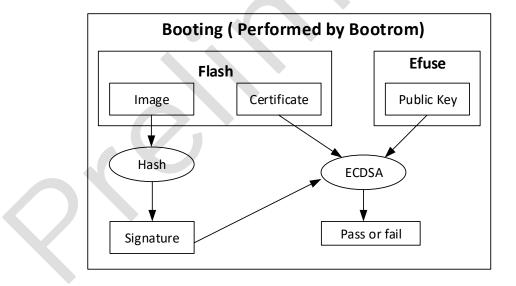

#### 3.7.2. Secure boot

The device supports secure boot based on user's choice. To support secure boot, a firmware image needs to be signed by an encrypted signature (called certificate) attached with that firmware image, as shown in *Figure* 17. During cold boot, the bootrom authenticate the signature.

If the authentication fails, the bootrom stops the booting process. The device has dedicated hardware engine and bootrom code to support secure boot.

As shown in *Figure* 17, to support secure boot, a signature must be generated using certain hash engine such as SHA-2. The signature is then encrypted by using ECC (elliptic curve cryptography) encryption. The encrypted signature is a certificate. That certificate will be attached to the image and be programmed into the device's flash memory. The signature is encrypted by using a private key. The corresponding public key shall be programmed into the IN618 internal eFuse memory, and the eFuse can be configured to lock the public key so that it cannot be modified or altered.

During cold boot, the bootrom hashes the image on the flash memory to calculate its signature. Then, the bootrom uses the ECDSA (Elliptic Curve Digital Algorithm) to authenticate and verify the signature based on the certificate, and the public key. If the verification process passes through, the bootrom will boot the image.

Figure 17 : Secure boot

## 4. Electronical Characteristics

There are voltage ranges where different VDDIO levels apply. The reason for this separation is for the IO drivers whose drive strength is directly proportional to the IO supply voltage. In the device, there is a large gap in the IO supply voltage range (1.7 to 3.6v). A guarantee on drive strength across this voltage range would be intolerable to most vendors who only use a subsection of the IO supply range. As such, these voltages are segmented into three manageable sections referenced as VDDIOL, VDDIOM, and VDDIOH in tables listed in this document.

## 4.1. Absolute maximum ratings

The values listed in this section are the ratings at which the chip can peak, and stresses listed above the absolute maximum rating may cause permanent damage to the device. Functional operation of the device should follow the conditions indicated in the "Recommended Operating Conditions", prolonged exposure to the absolute maximum rating may affect the reliability of the device.

| Description                     | Comments                                                | Min.  | Max.      | Unit |

|---------------------------------|---------------------------------------------------------|-------|-----------|------|

| Supply voltage (VDDI01, VDDI02) |                                                         | -0.3  | 3.9       | V    |

| Supply voltage (VBAT)           |                                                         | -0.3  | 3.9       | V    |

| Digital GPIO input              | All digital GPIO pins                                   | -0.3  | VDDIO+0.3 | V    |

| Analog HV input                 | CHIP_EN                                                 | -0.3  | VBAT      | V    |

| TRX supply voltage              | VDD_RF_2G4, VDD_VCO_2G4,<br>VDD_PLL, VDD_AMS            | -0.3  | 2         | V    |

| Analog LV input                 | XO_N, XO_P, RTC_XO_N,<br>RTC_XO_P, ADC_IN<br>*MGPIO_2_X | -0.3  | 2         | V    |

| Input RF level                  | RF_TRX_2G4                                              |       | 5         | dBm  |

| ESD human body model            | All pins                                                | -4000 | 4000      | V    |

| Storage temperature             |                                                         | -65   | 150       | °C   |

Note:\* The MGPIO\_2\_X Used as ADC input, the input voltage should be less than 2V.

## 4.2. Recommended operating conditions

| Description            | Min. | Тур. | Max. | Unit |

|------------------------|------|------|------|------|

| I/O supply voltage     | 1.7  | 3    | 3.6  | V    |

| Battery supply voltage | 1.7  | 3    | 3.6  | V    |

| Operating temperature  | -40  |      | 85   | °C   |

Table 5 : Recommended operating conditions

## 4.3. GPIO PAD characteristics

Measured at the following condition: Ta = 25°C, VBAT = 3.0V, L=4.7uH, C=4.7uF, unless otherwise noted.

| Parameter                      | Description                                                          | Min.       | Тур. | Max.      | Unit |

|--------------------------------|----------------------------------------------------------------------|------------|------|-----------|------|

| VIL                            | Input low voltage                                                    |            |      | 0.3*VDDI0 | V    |

| VIH                            | Input High voltage                                                   | 0.7*VDDI0  |      |           | V    |

| VOL                            | Output low voltage                                                   |            |      | 0.4       | V    |

| VOH                            | output high voltage                                                  | VDDIO-0.4V |      |           | V    |

| ЮН                             | Output high drive current                                            |            | 4    |           | mA   |

| IOS                            | Output standard drive<br>current                                     |            | 4    |           | mA   |

| tLH/tHL<br>(standard<br>drive) | Rising time/Falling time<br>@standard drive with 12pf<br>load10%~90% |            |      | 4         | ns   |

| tLH/tHL<br>(high drive)        | Rising time/Falling time<br>@high drive with 12pf load<br>10%~90%    |            |      | 3         | ns   |

| RPU                            | GPIO pull-up resistance                                              |            | 21K  |           | Ohm  |

| RPD                            | GPIO pull-down resistance                                            |            | 25K  |           | Ohm  |

Note: The data measured are preliminary and subject to change.

## 4.4. Buck converter characteristics